Q: 数据与指令均以二进制的方式存放在存储器中

CPU 如何区分得到的是数据还是指令?

A: 根据指令周期的不同阶段

执行阶段为数据

取指阶段为指令

Q: 设置当前工作目录主要作用是什么?

A: 加快文件检索速度

Q: 什么是指令预支技术?

A: 在该指令周期之前, 已经取得了该周期要用到的指令

Q: 指令周期和 CPU 时钟周期的大小关系

A: 指令周期由多个 CPU 时钟周期组成

CPU 时钟周期是计算机内最小的时间单位

Q: 系统抖动 (trashing) 是什么?

A: 一个页面刚被换出, 又要被换进主存

Q: 如何有效避免抖动?

A: 撤销部分进程

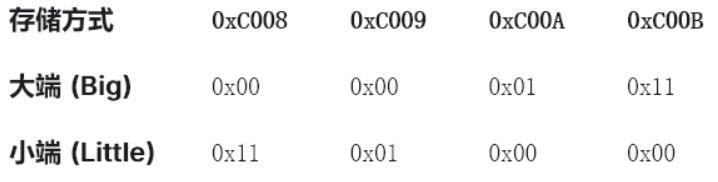

Q: 大端存储与小端存储

地址为字节编码, 数据为 Ox00000111

分别说明大端与小端存储情况

地址从 OxC008 开始

A:

大端存储与小端存储的记忆口诀

大端: 低地址存{c1: 大头}

小端: 低地址存{c1: 小头}

Q: 原语是用硬件实现还是软件实现?

A: 硬件实现或者软件结合硬件实现

似乎

Q: 多路选择器的作用

A: 从多个输入中选择一个输出

Q: 多路选择器与地址译码器有什么区别

A: 多路选择器: 从多个输入中选择一个输出

地址译码器: 根据输入, 从多个输出中选择一个激活

Q: 为什么多周期 CPU 的控制电路

比单周期 CPU 的控制电路更加复杂?

A: 多周期 CPU 需要进行多个时钟周期内相互配合

工作频率与时钟频率的关系

工作频率={时钟频率* 时钟传输次数}

{上下文切换} 实际上就是 {进程切换}

虚拟机监控程序的特权级为 {level -1}

操作系统特权级为 {level 0}

虚拟文件系统 VFS 的作用

为{不同文件系统}提供了统一的访问接口

Q: swap 分区开辟在内存上还是外存上?

A: 外存上

将外存上的一部分区域定义为 swap 区

作为物理内存的补充

当物理内存不够用的时候, 就将不活跃的内存数据放回到 swap 区中

Q: 对文件进行 open () 操作, 会将文件的什么东西读入内存?

A: 文件的 FCB

不会将整个文件读入

Q: disk buffer 开辟在内存上还是外存上?

A: 内存上

内存中的一部分用作 disk buffer 区

用于存储经常访问的磁盘数据

Q: 创立 disk buffer 主要是为了什么?

A: 减少读取磁盘的次数

减少 IO 时间

中断响应发生在{指令}执行结束后

DMA 响应发生在{总线事务}执行结束后

Q: 为什么 DMA 响应发生在总线事务执行结束之后? (过早/过迟)

A: 如果选择在指令完成之后, 再响应 DMA 请求, 可能发生数据丢失

如果选择在总线事务执行时候响应 DMA 请求, 可能发生数据出错

页分配算法

固定分配: 进程获得的页框数量{固定}, 在进程开始时确定

可变分配: 进程获得的页框数量{不固定}, 在进程运行时变化

页置换算法

当进程发生缺页中断时

局部置换: 只能从{该进程已分配的物理块}中选出一个页面进行置换

全局置换: 可以从{系统中的空闲物理块队列或其他进程的物理块}中选出一个页面进行置换.

Q: 某计算机主存地址空间大小为 64MB,现用多个 RAM 芯片组成了 32MB 的主存储器。按字节编址。

问:存储器地址寄存器 MAR 的位数至少是多少?

A: 26 位

- MAR 位数由地址空间 (64MB) 决定,而非实际安装容量 (32MB)。

- 计算:

。 - 所以需要 26 位地址线。

高级流水线的实现方式

超标量:{多套硬件}

超流水线:{拆分流水线}

超长指令字:{编译器多条指令打包成一条}

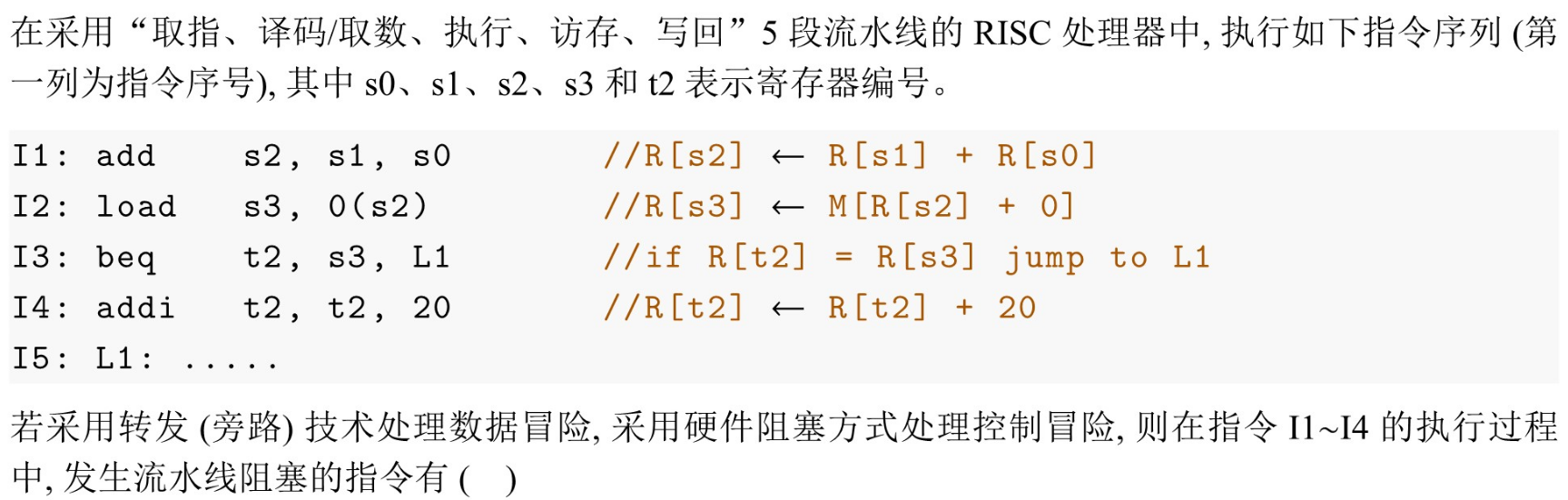

Q: 哪种数据冒险不能用转发旁路解决?

A: load-use 冒险

Q: 画出指令执行情况

A:

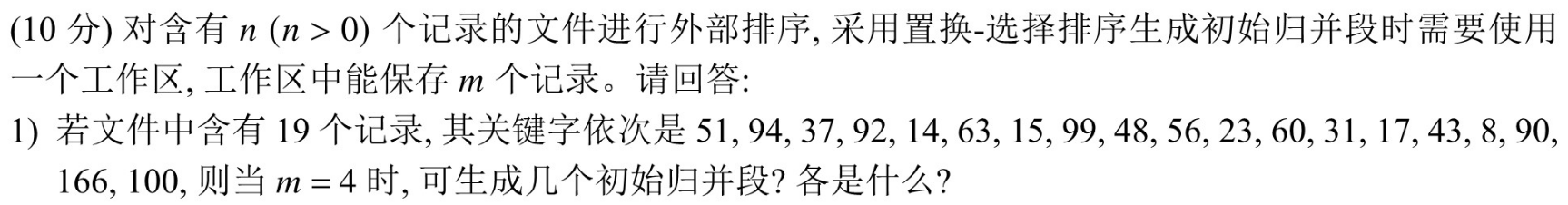

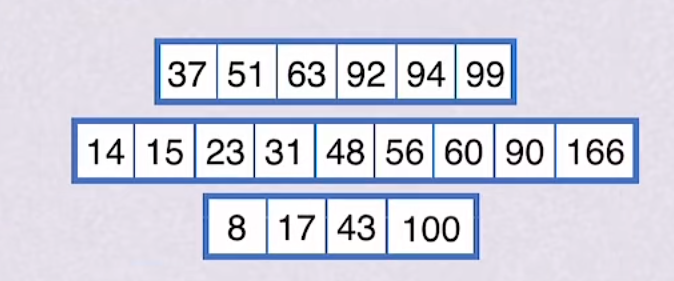

Q:

A:

Q: 进程 P 通过执行系统调用从键盘接收一个字符的输入,已知此过程中与进程 P 相关的操作包括:①将进程 P 插入就绪队列;②将进程 P 插入阻塞队列;③将字符从键盘控制器读入系统缓冲区;④启动键盘中断处理程序;⑤进程 P 从系统调用返回;⑥用户在键盘上输入字符

正确的操作顺序为?

A: ②,⑥,④,③,①,⑤

透明

Q: IR, MAR, MDR, PC, PSW,ACC, 通用寄存器(Rx), 基址(BR), 变址(IX)

程序员可以看到哪些?看不到哪些?

A: 看得到:PC, PSW,ACC, 通用寄存器(Rx), 基址(BR), 变址(IX)

看不到:IR,MAR,MDR

主存和 Cache 之间的数据调动是由硬件自动完成的, 对所有程序员均是透明的

主存和辅存之间的数据调动是由硬件和操作系统共同完成的, 对应用程序员是透明的, 对系统程序员不是透明的

分段对程序员来说是不透明的;

而分页对程序员来说是透明的

Cache 全由硬件实现, 是硬件存储器, 对所有程序员透明; 而虚拟存储器由 OS 和硬件共

同实现, 是逻辑上的存储器, 对系统程序员不透明, 但对应用程序员透明.

长度

MDR 的位数与数据线的位数相同, 数据线的位数通常等于存储字长, 因此 MDR 的位数通常等于存储字长

MAR 的位数与地址线的位数相同